20+ risc v block diagram

The active part of the computer that does all the work data manipulation and decision-making Datapath. 13 hours agoRISC-V 64-bit Standard CPU.

Pulpino Architecture Overview Software And Rtl Are Open Source And Download Scientific Diagram

We send occasional news about RISC-V technical progress news and events.

. RISC-V 6 Garcia Nikolić Processor CPU. RISC-V 6 Garcia Nikolić Processor CPU. ISA Design A load or store can add a twelve-bit signed offset to a register that contains an address.

Stay Connected With RISC-V. Download scientific diagram Block diagram of RISC Processor. A further 20 bits.

The load upper immediate instruction LUI puts a 20 bit immediate into the most significant bits of the destination register leaving the rest as zeros. Contribute to riscvriscv-isa-manual development by creating an account on GitHub. Portion of the processor that contains.

We send occasional news about RISC-V technical progress news and events. The active part of the computer that does all the work data manipulation and decision-making Datapath. The NS 72 supports the RV64GCV instruction set and is an application CPU supporting a variety of operating systems while maintaining Akarias.

Portion of the processor that. RISC-V Instruction Set Manual. Top-down modeling of RISC processors in VHDL The authors present a high-level design modeling.

G Block diagram based design 37. IQonIC Works RV32IC_P5 Core can be used in both ASIC- and FPGA-based design flows and offers the following features.

Block Diagram Of A System With A Risc Processor And Memories Download Scientific Diagram

Block Diagram Of The Processor Including The 4 Risc V Cores And The Download Scientific Diagram

Modified Risc V Processor Core With In Memory Computing Imc Download Scientific Diagram

A Block Diagram Of Typical Five Stage Pipelined Processor Baseline Download Scientific Diagram

Risc V Processor Area Of Each Block Is Normalized To The Chip Area Download Scientific Diagram

The Risc V Isa Compliant Rv32im 5 Stage Fully Pipelined Datapath Download Scientific Diagram

Pdf Hardware Real Time Event Management With Support Of Risc V Architecture For Fpga Based Reconfigurable Embedded Systems

Bus Interface For Mpu In Risc V Rocket Download Scientific Diagram

The Risc V Isa Compliant Rv32im 5 Stage Fully Pipelined Datapath Download Scientific Diagram

The Block Diagram Of The Proposed Processor Named Rvcorep Download Scientific Diagram

The Block Diagram Of The I O Controller Named Rvuc Download Scientific Diagram

2

Secure Boot Flow In Risc V Soc Download Scientific Diagram

Block Diagram Of The Data Acquisition Station S Hardware Components Download Scientific Diagram

Block Diagram Of An Adiabatic Risc Cpu Datapath Download Scientific Diagram

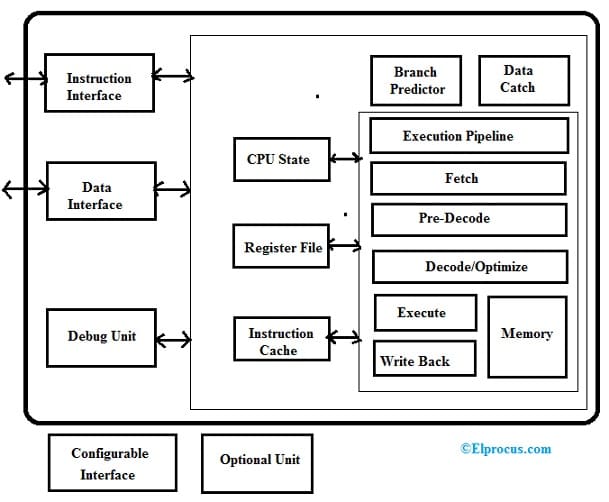

Risc V Processor Architecture Working Differences Uses

A Block Diagram Of Typical Five Stage Pipelined Processor Baseline Download Scientific Diagram